# EEEN203 Circuits Analysis Lab 1 SPICE

#### Due Friday, 15 March 2024

#### 1 Introduction

In this lab you will create a circuit schematic in LTspice and run a DC operating point analysis to find the DC voltages and currents at various points in your circuit.

You will also have run a transient analysis, which will show you how voltages and currents within the circuit change with time. These values should be comparable to those found via manual circuit analysis techniques that you have learnt in EEEN203 lectures.

#### 2 Background

SPICE, or Simulation Program with Integrated Circuit Emphasis, is open source software originally developed at UC Berkeley to aid the design and analysis of analogue electronics circuits.

Versions of SPICE, both open source and proprietary, are used throughout academia and industry to aid the design of electronic circuits.

Popular freeware versions include LTspice (Windows and OS X), maintained by Linear Technology and developed to aid the design of switch mode power supplies, and TINA-TI, developed by Texas Instruments (Windows only) and notable for its inclusion of accurate models for each of TI's components.

Common proprietary variants that you may encounter in industry include PSPICE, by Cadence, and National Instruments' MultiSim.

Additionally, online versions of SPICE are readily available at numerous websites, but may not be as well supported.

Apart from its speed and versatility, one of the main factors that makes SPICE a de facto standard for circuit simulation is that it can be extended to model new components via inclusion of an appropriate model file (file extension .MOD).

Most component manufacturers publish model files for their devices, which can be downloaded freely from the web.

Companies such as Linear Technology and Texas Instruments differentiate their SPICE programs by bundling model files for each of their components, minimising the need to download additional models.

The labs in EEEN203, and in other electronics courses at VUW such as 303, 403, and 405, all use LTspice for circuit modelling.

You might need to search a bit on the lab computers to find the executable (in the past it has been at C:\Program Files\LTC\LTspiceIV\XVIIx64.exe but this may change).

Alternatively, you can install LTspice on your own machine by downloading the relevant package from

| Abbreviation | Name  | Value      | Abbreviation | Name                   | Value     |

|--------------|-------|------------|--------------|------------------------|-----------|

| m            | milli | $10^{-3}$  | k            | kilo                   | $10^{3}$  |

| u            | micro |            | MEG          | mega                   | $10^{6}$  |

| n            | nano  | $10^{-9}$  |              | giga                   | $10^{9}$  |

| р            | pico  | $10^{-12}$ | Т            | $\operatorname{terra}$ | $10^{12}$ |

| f            | femto | $10^{-15}$ |              |                        |           |

Table 1: SPICE abbreviations for component values. Note case sensitivity.

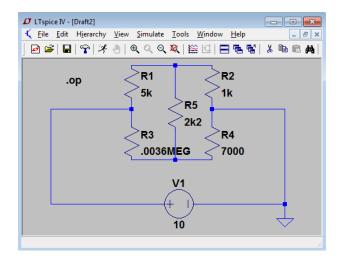

Figure 1: A series and parallel resistor circuit.

linear.com/designtools/software/#LTspice. It is cross-platform, available free of charge, and does not have a node limit.

# 3 Getting Started with LTspice

To find your way around the software, follow the official getting started guide available from the EEEN203 wiki page. Simon Bramble also maintains a series of excellent tutorials on LTspice (simonbramble.co. uk/lt\_spice\_lt\_spice.htm), Part 1 is most relevant for the work we will do in EEEN203.

#### 4 Schematic Entry

- Recreate the circuit shown in Figure 1 by clicking on the various component icons in the LTspice toolbar and then clicking to place various components on your schematic. Once you have a component on your schematic, you can right click on it to set its properties and value. Note that SPICE (including LTspice) uses a non-standard way of specifying value multipliers, shown in Table 1.

- The voltage source at the bottom of Figure 1 can be found by clicking on the "Component" button (just to the left of the "Move" hand on the toolbar) and selecting the "voltage" component from the base symbol library (possibly at C:\Program Files (x86)\LTC\LTspiceIV\lib\sym\ on Windows).

- You can rotate a component using Ctrl-R before you place it.

- Finally, take extra care to add a ground reference point to your circuit: this is the *only* component that is common to every single SPICE circuit, and it is essential for your model to run.

If you get stuck, refer to pp. 14–27 in the LTspice getting started guide for help.

# 5 Manual Calculations

Before moving on to the next step, use any of the circuit analysis techniques you have learnt in EEEN203 to find the current through the  $1 k\Omega$  resistor, R2, in your circuit.

Make a note of roughly how long it takes you to perform this calculation.

# 6 Simulation

To run a simulation, you need to specify the type of analysis to be performed. The options are:

- Transient analysis

- Small signal AC analysis

- DC sweep

- Noise

- DC transfer function

- DC operating point

The DC operating point, transient, and Small signal AC analyses will be most useful for us in EEEN203.

For now, choose "Edit Simulation Cmd" from the Simulate menu and select "DC op pnt" to find the DC operating point of the circuit. Click OK, and then click again near your circuit to place the text string (".op") required to perform your select analysis. As you become more comfortable with LTspice, you will learn the simulation string syntax and be able to specify simulation commands directly as text strings, rather than using the "Edit Simulation Cmd" window.

Click "Run" in the Simulate menu to run your simulation. A window will pop up listing the voltages and current at different points in your circuit. It can be a little confusing at first to work out how values in the window correspond to points on your circuit, but paying careful attention to your component names should give you enough of a clue to work out what's going on. Another handy piece of information to know is that positive currents are defined as travelling *into* the list component.

Check the current flowing through R2.

Is this the same current that you calculated earlier?

Which method (manual calculation or LTspice simulation) allowed you to find the current faster?

To make it a fair comparison, consider the time it took to enter the circuit into LTspice and configure the simulation, as well as the time you spent checking your working when doing the calculation manually.

# 7 More Simulation

Although the DC operating point simulation gives all of the information that you need to verify your manual circuit analyses, the results could be presented in a more intuitive manner.

A useful thing to do is to run a transient analysis, which will create graphs showing how the voltages and currents in your circuit change with time.

Although we do not expect any change with time from a purely DC source in a purely resistive circuit (i.e. the graphs will all be straight lines), this analysis is useful because it allows us to point and click on circuit nodes (for voltages) or components (for currents) and see the related quantities displayed on the plot.

This is a much more intuitive way of displaying information than the text document style favoured by DC operating point analysis.

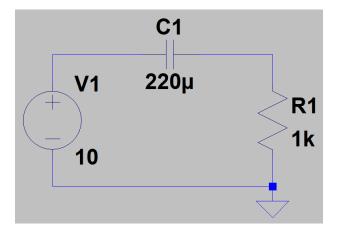

Figure 2: A simple RC circuit.

To run a transient analysis, select "Edit Simulation Cmd" from the Simulate menu and select the Transient tab.

Specify a stop time (this is arbitrary, but must be a number greater than 0).

Notice that the command window is populated once you enter a stop time, and that the string in this window (.tran 1 or similar) is copied onto your circuit when you click OK.

You can now delete the DC operating point simulation command (.op) from your circuit if you like.

#### 8 More on Transients

Transient analyses will become much more important later in the term when we look at resistor-inductor (RL) and resistor-capacitor (RC) circuits, shown in Figure 2.

One of the things we will learn is that the *time constant*,  $\tau$ , of such circuits is given by

$$\tau = RC \tag{1}$$

$$=\frac{L}{R}$$

(2)

for circuits made up of a resistor, R, and capacitor, C, or a resistor, R, and inductor, L, respectively.

Here the relevant units are ohms for R, Farads for C, and Henries for L.

But what is the physical meaning of  $\tau$ ?

It is the time taken for the voltages and currents to reach a certain percentage of their final values. Can you use what you have learnt about LTspice to implement the circuit shown in Figure 2 and find what percentage this is?

Once you have found a value, do some search or some maths to find the mathematical basis for this magical percentage.

Note: to find meaningful answers you will need to select "Start external DC supply voltages at 0V" in the Edit Simulation Cmd window, as shown in Figure 3.

#### 9 Conclusion

SPICE is a powerful tool for designing, refining, and understanding analogue circuits.

You can use it to check manual analyses as well as test drive circuits before production.

| Transient                    | AC Analysis                                                                                                                                                                                                          | DC sweep                                                                                                                                                             | Noise                                                                                                                       | DC Tra   | ansfer                                                                  | DC op pnt              |    |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------|------------------------|----|--|

|                              |                                                                                                                                                                                                                      | orm a non-lin                                                                                                                                                        | ear, time-                                                                                                                  |          |                                                                         |                        |    |  |

| Stop Time: 1                 |                                                                                                                                                                                                                      |                                                                                                                                                                      |                                                                                                                             |          |                                                                         |                        |    |  |

| Time to Start Saving Data: 0 |                                                                                                                                                                                                                      |                                                                                                                                                                      |                                                                                                                             |          |                                                                         |                        |    |  |

|                              |                                                                                                                                                                                                                      | Maximu                                                                                                                                                               | ım Times                                                                                                                    | tep: .00 | 001                                                                     |                        |    |  |

| 9                            | Start external D                                                                                                                                                                                                     | C supply vol                                                                                                                                                         | tages at I                                                                                                                  | IV: 🔽    |                                                                         |                        |    |  |

| St                           | op simulating i                                                                                                                                                                                                      | f steady state                                                                                                                                                       | is detec                                                                                                                    | ted: 📃   |                                                                         |                        |    |  |

| Don't r                      | eset T=0 wher                                                                                                                                                                                                        | n steady state                                                                                                                                                       | is detec                                                                                                                    | ted: 📃   |                                                                         |                        |    |  |

|                              | Ste                                                                                                                                                                                                                  | p the load cu                                                                                                                                                        | rrent sou                                                                                                                   | rce: 📃   |                                                                         |                        |    |  |

|                              | Skip Initia                                                                                                                                                                                                          | al operating p                                                                                                                                                       | oint solut                                                                                                                  | ion: 📃   |                                                                         |                        |    |  |

| iyntax: .tra                 | n <tprint> <ts< td=""><td>top&gt; [<t start<="" td=""><td>&gt; [<tmax< td=""><td>step&gt;]]</td><td>(<option< td=""><td>i&gt; (<option></option></td><td>]]</td></option<></td></tmax<></td></t></td></ts<></tprint> | top> [ <t start<="" td=""><td>&gt; [<tmax< td=""><td>step&gt;]]</td><td>(<option< td=""><td>i&gt; (<option></option></td><td>]]</td></option<></td></tmax<></td></t> | > [ <tmax< td=""><td>step&gt;]]</td><td>(<option< td=""><td>i&gt; (<option></option></td><td>]]</td></option<></td></tmax<> | step>]]  | ( <option< td=""><td>i&gt; (<option></option></td><td>]]</td></option<> | i> ( <option></option> | ]] |  |

| tran 0 1 0 .                 | 0001 startup                                                                                                                                                                                                         |                                                                                                                                                                      |                                                                                                                             |          |                                                                         |                        |    |  |

|                              |                                                                                                                                                                                                                      |                                                                                                                                                                      |                                                                                                                             |          |                                                                         |                        |    |  |

Figure 3: Simulation setup to find time constants.

Note, however, that a circuit's behaviour is affected by more than just the order that its components are connected in.

This means that simulation cannot be used to completely replace bread-boarding and prototyping circuits.

The reasons behind this limitation are explored in EEEN303: Analogue Electronics.

#### 10 To hand in

You need to hand in a write-up including an Aim, Method and Conclusion, and enough of your working to show that you've completed the lab.

- 1. Aim: a short introduction describing and motivating the task (why is it important),

- 2. Methods: a theoretical section describing in more detail the task at hand and the approach (the methods) taken (this section usually includes equations), and

- 3. Results: a section that describes the results, and a discussion of what they mean. This will include some screen shots, and some working for the manual solution.

#### Marking schedule (out of 7):

1 mark for reproducing each of the Figures 1 and 2 in the lab script.

1 mark for the manual calculation

Then 1 mark for each of the usual sections:

- 1. Aim: a short introduction describing and motivating the task (why is it important),

- 2. Methods: a theoretical section describing in more detail the task at hand and the approach (the methods) taken(this section usually includes equations), and

- 3. Results: a section that describes the results, and a discussion of what they mean

1 mark for overall presentation and structure.